一文讀懂EMC測試實質(四)

值得注意的是,ESD接觸放電電流波形的上升沿時間會在1 ns以下,這意味著ESD是一種高頻現象。ESD放電電流路徑與大小不但由EUT的內部實際連接關系(這部分連接主要在電路原理圖中體現)決定,而且還會受這種分布參數的影響。圖6表達了某一產品進行ESD測試時的ESD放電電流分布路徑。圖6中的CP1、CP2、CP3分別是放電點與內部電路之間的寄生電容、電纜與參考接地板之間的寄生電容和EUT殼體與參考接地板之間的寄生電容。這些電容的大小都會影響各條路徑上的ESD電流大小。

如果有一條ESD電流路徑包含了產品的內部工作電路,那么該產品在進行ESD測試時受ESD的影響就會很大;反之則產品更容易通過ESD測試。可見,如果產品的設計能避免ESD共模電流流過產品內部電路,那么這個產品的抗ESD干擾的設計是成功的,ESD抗擾度測試實質上包含了一個瞬態共模電流(ESD電流)流過產品(瞬態共模電流)干擾正常工作電路的原理。

其次,ESD測試時所產生的ESD電流還伴隨瞬態磁場,當這種時變的磁環經過電路中的任何一個環路時,該環路中都會產生感應電動勢,從而影響環路中的正常工作電路。四、共模傳導性抗擾度測試實質共模抗擾度測試以共模電壓的形式把干擾疊加到被測產品的各種電源端口和信號端口上,并以共模電流的形式注入到被測產品的內部電路中(產品的機械結構構架對EFT/B共模電流的路徑與大小起著決定性的作用,或直接以共模電流的形式注入到被測產品的內部電路中,共模電流在產品內部傳輸的過程中,會轉化成差模電壓并干擾內部電路正常工作電壓(產品電路中的工作電壓是差模電壓)。

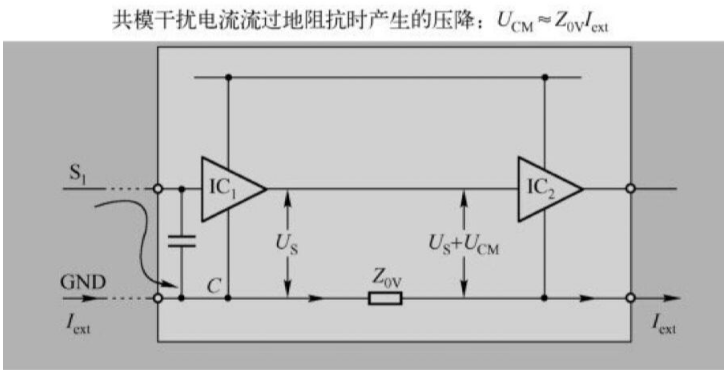

對于單端傳輸信號,如圖1所示,當同時注入到信號線和GND地線上的共模干擾信號進入電路時,在IC1的信號的端口處,由于S1于GND所對應的阻抗不一樣(S1 較高,GND較低),共模干擾信號會轉化成差模信號,差模信號存在于S 1 與GND之間。這樣,干擾首先會對IC1的輸入口產生干擾。濾波電容C的存在,使IC1 的第一級輸入受到保護,即在IC1 的輸入信號端口和地之間的差模干擾被C濾除或旁路(如果沒有C的存在,可能干擾就會直接影響IC1的輸入信號),然后,大部分會沿著PCB中的低阻抗地層從一端流向地層的另一端,后一級的干擾將會在干擾電流流過地系統時產生(當然這里忽略了串擾的因素,串擾的存在將使干擾電流的流徑路徑復雜化,因此串擾的控制在EMC設計中也是非常重要的一步)。

圖7共模干擾電流流過地阻抗時產生的壓降

其中,圖7中的Z0V表示PCB中兩個集成電路之間的地阻抗,US表示集成電路IC1向集成電路IC2傳遞的信號電壓。共模干擾電流流過地阻抗 Z0V時,Z0V的兩端就會產生壓降 UCM≈Z0V Iext。該壓降對于集成電路IC 2 來說相當于在IC 1 傳遞給它的電壓信號 U S 上又疊加了一個干擾信號U CM,這樣IC 2 實際上接受到的信號為U S+U CM,這就是干擾。干擾電壓的大小不但與共模瞬態干擾的電流大小有關,還與地阻抗 Z0V的大小有關。當干擾電流一定的情況下,干擾電壓UCM的大小由Z0V決定。也就是說,PCB中的地線或地平面阻抗與電路的瞬態抗干擾能力有直接影響。

例如,一個完整(無過孔、無裂縫)的地平面,在100 MHz的頻率時,只有3.7 mΩ的阻抗。即使有100 A的瞬態電流流過3.7 mΩ 的阻抗,也只會產生0.37 V的壓降,這對于3.3 V的TTL電平的電路來說,是可以承受的,因為3.3 V的TTL電平總是要在0.8 V以上的電壓下才會發生邏輯轉換,這已經是具有相當的抗干擾能力了。又如,流過電快速瞬變脈沖群干擾的地平面存在1 cm的裂縫,那么這個裂縫將會有1 nH的電感,這樣當由100 A的電快速瞬變脈沖群共模電流流過時,產生的壓降:V= | L×dI/dt| =1 nH×100 A/5 ns=20 V20 V的壓降對3.3 V電平的TTL電路來說是非常危險的,可見PCB中地阻抗對抗干擾能力的重要性。

實踐證明對于3.3 V的TTL電平邏輯電路來說,共模干擾電流在地平面上的壓降小于0.4 V將是安全的;如果大于2.0 V將是危險的。對于2.5 V的TTL電平邏輯電路,這些電壓將會更低一點(0.2V和1.7V),從這個意識上,3.3V TTL電平的電路比2.5V電平的TTL電路具有更高的抗干擾能力。

對于差分傳輸信號,當共模電流ICM流過地平面時,必然會在地平面的阻抗Z0V兩端產生壓降,當共模電流ICM一定時,地平面阻抗越大,壓降越大。像單端信號被干擾的原理一樣,這個壓降猶如施加在差分線的一根信號線與參考地之間,即圖8中所示的 UCM1、UCM2、UCM3、UCM4。

圖8 共模干擾電流對差分電路的干擾原理

由于差分線對的一根線與參考地之間的阻抗Z1、Z2,接收器與發送器的輸入/輸出阻抗Z S1、Z S2,總是不一樣的(由于寄生參考的影響,實際布線中不可能做到兩根差分線對的對地阻抗一樣),從而造成UCM1、UCM2、UCM3、UCM4的值也不相等,差異部分即轉化為差模干擾電壓Udiff,對差分信號電路產生干擾。可見,對于差分電路來說,地平面的阻抗也同樣重要,同時PCB布線時,保證差分線對的各種寄生參數平衡一致也很重要。

五、差模傳導性抗擾度測試實質

差模傳導性抗擾度測試原理非常簡單,測試時,差模干擾電壓直接疊加在正常工作電路上,然后觀察電路工作是否正常。由于單一的差模傳導性抗擾度測試通常都是低頻的測試,而且都是針對瞬態干擾的抗擾度測試,這樣傳遞干擾路徑的分析也比較容易,因為較小的寄生參數不會對低頻信號傳輸產生較大的影響。六、差模共模混合的傳導性抗擾度測試實質差模共模混合的傳導性抗擾度測試主要是指,在傳導性抗擾度測試中,既要進行差模測試又要進行共模測試,或在差模過程中既有共模的干擾直接注入到產品被測端口上,又有差模的干擾直接注入到產品被測端口上的傳導性抗擾度測試。

-

技術原理

-

科技前沿

-

科技前沿

-

綜述

-

焦點事件